Stage - Développement d’un accélérateur matériel pour la PQC, sécurisé contre les attaques par canaux auxiliaires

Le poste

Descriptif du poste

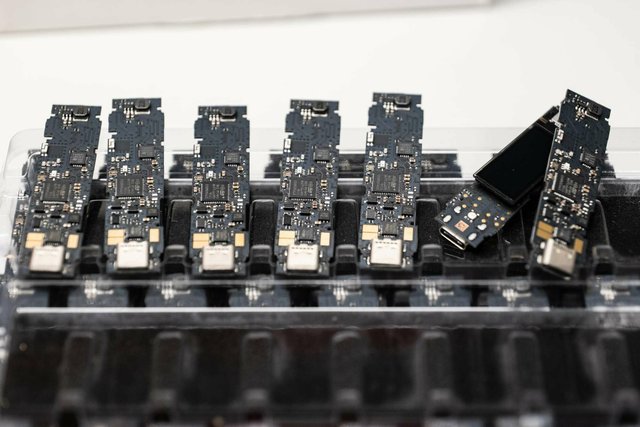

Au sein de la division Scientifique et Technique de la sous-direction Expertise, le laboratoire Sécurité des Composants (LSC) intervient dans le domaine de composants sécurisés et des logiciels qu’ils embarquent. Le laboratoire a pour objectif d’anticiper les risques, de soutenir le centre de certification national lors des évaluations des produits de sécurité, de contribuer à la recherche, à l’analyse des besoins et à la conception de solutions propres à les satisfaire.

Contexte du stage

Avec l’arrivée envisagée à moyen terme d’un ordinateur quantique, les algorithmes cryptographiques classiques, comme RSA ou ECC, ne permettent plus de garantir la sécurité des informations. La cryptographie post-quantique (PQC) émerge comme une solution essentielle pour sécuriser les communications et les données à long terme. Cependant, les algorithmes PQC, souvent plus complexes, nécessitent des ressources de calcul accrues, limitant leur déploiement sur des systèmes embarqués ou à haute performance. Dans ce contexte, le développement d’accélérateurs matériels dédiés apparaît comme une piste prometteuse pour concilier sécurité et efficacité. Ce stage s’inscrit dans cette dynamique, visant à concevoir et optimiser un accélérateur matériel pour un algorithme de cryptographie post-quantique, afin d’en améliorer les performances tout en garantissant sa robustesse face aux attaques matérielles.

Objectifs du stage

La mission du candidat sera d’étudier la faisabilité d’un bloc matériel générique de calcul de la primitive de hachage SHA3/Keccak dans le contexte spécifique de son utilisation comme primitive au sein d’algorithmes cryptographiques post-quantiques (ML-KEM/ML-DSA).

Le candidat devra :

prendre en main la spécification des algorithmes DiLithium et Kyber standardisés sous les noms ML-DSA et ML-KEM, en se focalisant sur l’instanciation de la primitive SHA3 dans leur flot de calcul ;

dresser un panorama de l’état de l’art des architectures existantes et des schémas de masquage existants par une étude bibliographique rigoureuse ;

à partir de cet existant, mener une réflexion personnelle et se montrer force de proposition sur l’architecture RTL générique à donner à un bloc de calcul SHA3 adapté à DiLithium et Kyber ;

développer une première preuve de concept fonctionnelle (en VHDL ou en Verilog, sur cible FPGA).

Si le temps le permet, le stagiaire pourra approfondir certains éléments comme le schéma de masquage applicable, la rédaction d’un document de définition d’architecture du bloc ou encore l’analyse des performances.

Profil recherché

Le candidat est en dernière année d’école d’ingénieur ou cursus universitaire, dans le domaine des nouvelles technologies (informatique, mathématiques, électronique). Le stage sera orienté recherche, une appétence pour le domaine de la sécurité matérielle et l’envie de développer sur des circuits électroniques en laboratoire seront attendues.

Compétences requises :

Compétences solides en informatique bas niveau ;

Maîtrise de la conception matérielle et d’au moins un langage de programmation de type VHDL ou Verilog ;

Des connaissances en cryptographie et/ou attaques par canaux auxiliaires seront appréciées.

Qualités :

Curiosité d’esprit et rigueur ;

Appétence pour les sujets techniques et complexes ;

Autonomie ;

Capacité de rédaction et de synthèse ;

Sens du service public.

Déroulement des entretiens

· Si votre candidature est présélectionnée, vous serez contacté(e) pour apprécier vos attentes et vos motivations au cours d’un entretien téléphonique ou physique.

· Vous pourrez faire l’objet d’une procédure d’habilitation.

Envie d’en savoir plus ?

Rencontrez Nicolas, Chef de projet de cyberdéfense

Rencontrez Alexandre, Chef de bureau adjoint Ingénierie du cadre normatif

D’autres offres vous correspondent !

Ces entreprises recrutent aussi au poste de “Ingénierie matérielle”.

Stage Système embarqués : Etude d'un dispositif de sécurité sans fil F/H

MBDA FranceStageLe Plessis-RobinsonTélétravail non autoriséCybersécurité, Aéronautique / Spatiale7 900 collaborateursFirmware Engineer - Internship

LedgerStageParisTélétravail fréquentFinTech / InsurTech, Blockchain637 collaborateursSTAGE - Qualification Composants & Circuit Imprimé F/H

ThalesStageMeudonLogiciels, Cybersécurité80 000 collaborateursStage : Ingénieur Vérification Asic R&D (F/H)

EvidenStageLes Clayes-sous-BoisTélétravail fréquentSalaire : 19K à 20K €IT / Digital, SaaS / Cloud Services4 200 collaborateurs